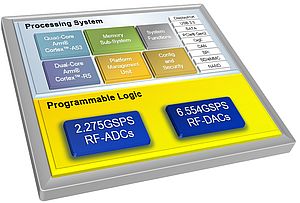

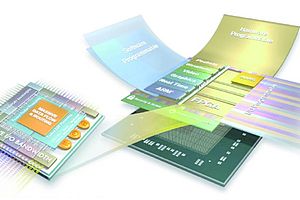

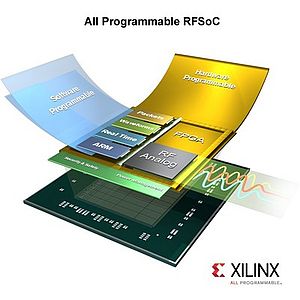

Xilinx ha annunciato un’integrazione rivoluzionaria e un’importante innovazione architetturale per il Wireless 5G con una tecnologia RF di classe analogica all’interno dei propri MPSoC interamente programmabili da 16nm. I nuovi RFSoC di Xilinx eliminano i convertitori dati discreti, forniscono una riduzione dei consumi e dell’ingombro del 50-75% nelle applicazioni radio massive di tipo MIMO 5G e nelle dorsali wireless a onde millimetriche.

Integrazione di ADC e di DAC

Le matrici di antenne 2D su grande scala saranno fondamentali per aumentare l’efficienza spettrale e la densificazione delle reti richiesta per il 5G. I produttori dovranno trovare nuovi modi per rispettare i rquisiti delle applicazioni commerciali. Con l’integrazione di ADC e di DAC ad alte prestazioni in un SoC interamente programmabile, le unità di dorsale radio e wireless possono soddisfare requisiti un tempo irraggiungibili in termini di potenza e di fattore di forma, aumentando al contempo la densità dei canali. Inoltre, i dispositivi RFSoC consentono di armonizzare i cicli di progettazione e di sviluppo per rispettare le tempistiche d’introduzione della tecnologia 5G.

Conversione dati RF

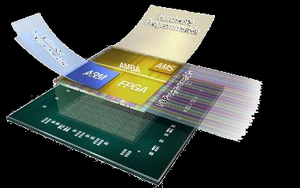

La tecnologia integrata di conversione dati RF basata sul processo da 16nm include:

• Campionamento RF diretto che semplifica la progettazione analogica, aumenta l’accuratezza riduce il fattore di forma abbattendo i consumi

• ADC a 12bit ADC fino a 4GSPS a elevato numero di canali con conversione di frequenza in digitale

• DAC a 14bit fino a 6,4GSPS a elevato numero di canali con conversione verso frequenze superiori

Il passaggio alla tecnologia FinFET combina una densità d’integrazione elevata con miglioramenti nelle prestazioni dei dispositivi analogici. L’inclusione dell’elaborazione dei segnali RF all’interno della soluzione SoC RFSoC IP consente ai clienti 5G di introdurre in commercio sistemi altamente differenziati per le applicazioni radio massive di tipo MIMO e per le dorsali wireless a onde millimetriche.